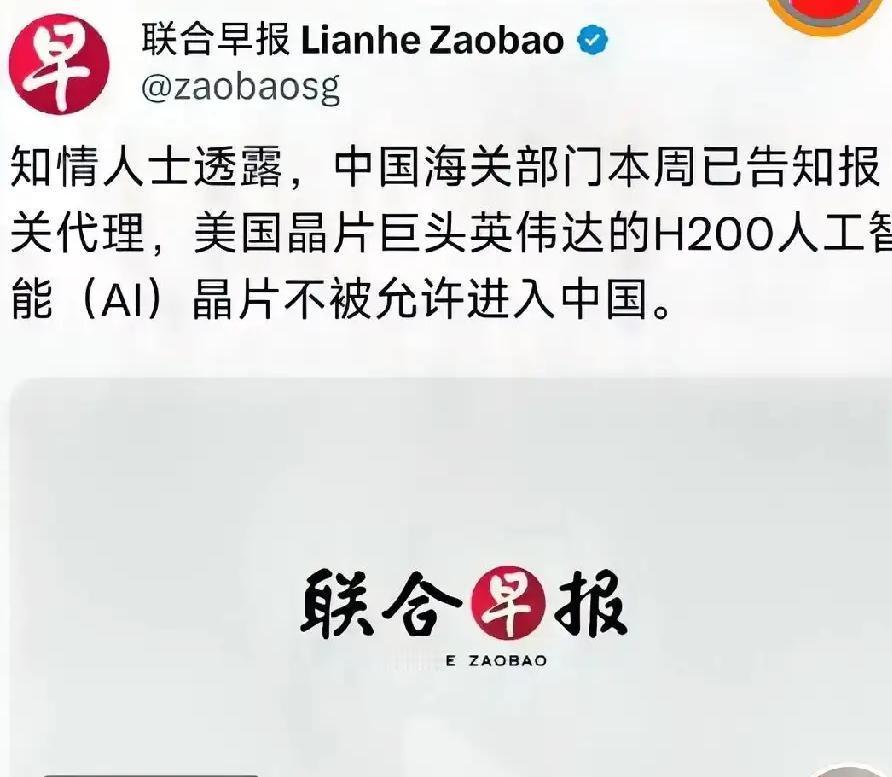

光刻机战场传来重磅消息!尼康突然甩出王炸,全球首台无掩膜光刻机横空出世,直接瞄准AI芯片封装环节,这招避开EUV正面战场的打法堪称绝妙。 麻烦看官老爷们右上角点击一下“关注”,既方便您进行讨论和分享,又能给您带来更多优质的内容,感谢您的支持! 过去二十年,全球半导体行业基本围着 “制程竞赛” 转,谁能做出更先进的芯片制程,谁就掌握话语权。在这场比拼中,荷兰 ASML 凭借 EUV 光刻机一骑绝尘,成为 7nm 及以下先进制程的唯一设备供应商,垄断了全球超 80% 的高端光刻设备市场。 台积电、三星、英特尔这些行业巨头,为了抢占先进制程高地,纷纷砸重金围绕 ASML 的 EUV 设备布局产能,形成了紧密的绑定关系。而曾经的光刻巨头尼康和佳能,在 EUV 技术赛道上逐渐掉队,不得不退出前沿制程竞争,转而在成熟制程领域寻找机会。 ASML 的 EUV 光刻机之所以能形成垄断,核心在于其技术壁垒高到难以逾越。这台设备集成了超 10 万个零部件,需要全球 5000 余家供应商协作,核心光学系统由德国蔡司独家供应,激光源来自美国 Cymer,整个技术迭代周期长达 10 年以上,行业内至今没有替代方案。 更关键的是,EUV 光刻机还深陷地缘政治漩涡,受进出口政策限制影响极大,不是有钱就能买到的设备。对于很多想要布局高端芯片的企业来说,EUV 光刻机不仅价格昂贵(单台售价最高突破 3 亿欧元),获取渠道还充满不确定性。 就在大家都以为光刻机市场会一直被 EUV 路线主导时,AI 芯片的崛起彻底改变了行业逻辑。现在芯片性能的提升,不再只靠缩小制程尺寸,Chiplet(芯粒)、2.5D 和 3D 封装等封装层面的创新,成为了算力增长的新引擎。 封装环节不再是芯片生产的 “后端辅助”,反而从幕后走到台前,成为决定 AI 芯片性能上限的关键环节。尤其是 AI 芯片对算力的需求越来越高,需要将多个芯粒、HBM 存储等异构集成,传统封装工艺已经难以满足大尺寸、高精度、快迭代的需求。 这个行业变革的风口,让尼康看到了突围的机会。2025 年,尼康正式发布全球首款专为半导体后道工艺设计的无掩模光刻系统 DSP-100,直接瞄准 AI 芯片封装环节,这步差异化竞争的棋下得堪称绝妙。 这款无掩模光刻机最核心的创新,就是彻底抛弃了传统光刻依赖的掩膜版。它采用空间光调制器(SLM)技术,通过数字化光学系统直接在基板上直写电路图案,不需要提前制作昂贵且耗时的掩模。 传统掩膜版不仅成本高,制作周期还长达数周,一旦芯片设计需要修改,整套掩膜都得重新制作,严重影响研发效率。而尼康的 DSP-100 能把设计迭代周期压缩至小时级,大大提升了 AI 芯片封装的定制化能力。 虽然它不追求 EUV 那样的极限线宽,分辨率达到 1 微米,但这完全能满足 AI 芯片封装的需求。更值得一提的是,它支持 600 毫米 ×600 毫米的超大基板,通过 16 组精密镜头阵列的实时校准,重合精度能控制在 ±0.3 微米以内,首次实现了大尺寸基板与微米级精度的兼容。 在效率和成本上,DSP-100 也展现出了碾压式优势。实测数据显示,它在 510 毫米 ×515 毫米基板上每小时可处理 50 片,较传统晶圆级封装方案效率提升 30% 以上;满负荷运行 600 毫米全尺寸基板时,单位面积产能达到 300 毫米晶圆的 9 倍,单颗 AI 加速器封装成本能降低 50%。 为了适应封装工艺的复杂需求,DSP-100 还搭载了三大核心技术:动态形变补偿系统能实时调整投射角度,压制翘曲导致的误差;固态 i 线光源寿命较传统汞灯延长 10 倍,维护间隔从 200 小时延至 2000 小时;封闭式光路设计则确保了设备长期稳定性。 尼康这招 “避其锋芒” 的打法,不仅避开了 EUV 光刻机的技术壁垒和地缘政治雷区,还充分发挥了日本在半导体材料、精密加工等领域的体系化优势。日本在这些基础领域的积累,为无掩膜光刻机的研发和量产提供了坚实支撑。 目前,DSP-100 已经启动全球预订,预计在 2026 年 3 月 31 日前正式交付客户。多家头部封测厂已经表达了订单意向,业内预计这款设备 2026 财年上市后,将迅速抢占 20% 的扇出型面板级封装(FOPLP)设备市场份额。 要知道,台积电计划 2027 年试产 FOPLP 技术,三星已经在 Galaxy Watch 芯片封装中验证了面板级封装的可行性,英特尔也在研发 600 毫米面板 3D 堆叠方案,尼康的 DSP-100 正好赶上了面板级封装从实验室走向量产的关键节点。