米勒效应是MOS管开关过程中栅漏电容(Cgd)通过放大作用在栅极感应出额外电荷,导致开关速度下降、损耗增加甚至误导通的现象。它并非完全"消除",而是通过电路设计与器件选型将其影响抑制到可接受范围。以下从原理、抑制策略到工程实践,系统阐述专业解决方案。

一、米勒效应的物理本质与危害

1.1 形成机制

在开关瞬态,漏极电压VDS从0跳变至Vbus(如400V),dVDS/dt可达10kV/μs。该变化通过Cgd耦合到栅极,产生感应电流:I_gd = Cgd × dVDS/dt

若Cgd=50pF,dVDS/dt=10kV/μs,则I_gd=500mA。该电流流入栅极节点,使VGS在米勒平台期(Vth+Id/gm)维持时间延长,开关损耗剧增。

1.2 主要危害

开关速度下降:米勒平台使tr/tf延长2-5倍,开关损耗增加50-200%

EMI恶化:平台期VDS与ID重叠,产生高频辐射

误导通风险:在桥式电路中,互补管开通时的dVDS/dt可能使关断管VGS超过Vth,导致桥臂直通

栅极击穿:感应电压叠加驱动电压,可能超过VGS_max(±20V)

二、抑制策略分类:从源头到路径的全方位拦截

2.1 器件级抑制:选择低Cgd器件

核心思想:Cgd是米勒效应的源头,减小Cgd是釜底抽薪。

技术实现:

屏蔽栅沟槽(SGT)技术:在沟槽栅底部增加屏蔽电极,将Cgd从50pF降至15pF,米勒电荷Qgd降低70%。如安森美的NTHD4N02R1,Qgd仅4nC,适合MHz级应用。

分裂栅结构:将栅极分为两段,阻断Cgd耦合路径,Cgd降低60%。

SiC/GaN器件:宽禁带材料本征Cgd低,1200V SiC MOSFET的Cgd<10pF,dVDS/dt耐受能力>50V/ns。

工程权衡:SGT结构虽降低Cgd,但增加工艺复杂度,成本提升20-30%。在100kHz以下应用中,性价比不如传统平面栅。

2.2 驱动级抑制:增强驱动吸收能力

核心思想:提供低阻抗泄放路径,将I_gd快速旁路到地,防止其在栅极积累。

方法A:栅极串联电阻Rg

Rg与Cgd构成RC低通滤波器,带宽f = 1/(2π×Rg×Cgd)。Rg从0Ω增至10Ω,带宽从∞降至318MHz,有效抑制高频耦合。

取值原则:

下限:Rg_min = (Vdrive - Vplat) / Ig_peak,确保驱动电流足够

上限:Rg_max = tr_max × Vdrive / Qg,防止开关过慢

推荐值:5-50Ω,独立调节开通与关断电阻(Rg_off < Rg_on)

工程实例:某48V/20A电机驱动中,Rg从0Ω增至15Ω,米勒平台宽度从200ns降至80ns,振铃从3Vpp降至0.5Vpp,效率仅下降1.5%,但EMI降低15dB。

方法B:栅源并联电容Cgs_ext

在栅源极间并联10-100pF小电容,与Cgd构成分压网络。Cgs_ext=50pF时,感应到栅极的电压分压比为Cgd/(Cgd+Cgs_ext),从100%降至25%。

代价:增加驱动电荷Qg_total = Qg + (Cgs_ext×VGS),驱动损耗增加30%。适用于Qg<20nC的小信号MOS管。

方法C:有源米勒钳位

在栅源极间并联一个小型MOSFET(如2N7002),当VGS>0.5V时导通,将栅极电位锁定在0V。响应时间<10ns,钳位阻抗<1Ω。

电路实现:钳位管栅极接驱动信号反相端,驱动关断时钳位管导通。成本仅增加0.1元,效果媲美-3V负压驱动。

2.3 电路拓扑级抑制:消除dVDS/dt

核心思想:降低漏极电压变化率,从根本上减小I_gd。

方法D:RCD缓冲电路

在漏源极并联R-C-D网络,阻尼VDS上升斜率。参数设计:

电容C:≈2×Coss,100pF-1nF

电阻R:R = √(L_parasitic / Coss),10-100Ω

二极管:快恢复二极管,t_rr<50ns

效果:某650V/50A逆变器中,RCD使dVDS/dt从10kV/μs降至3kV/μs,I_gd从500mA降至150mA,米勒平台缩短60%。

方法E:软开关拓扑

LLC谐振实现ZVS(零电压开关),VDS在电流过零后上升,dVDS/dt<500V/μs,米勒效应可忽略。这是终极解决方案,但增加谐振电感成本。

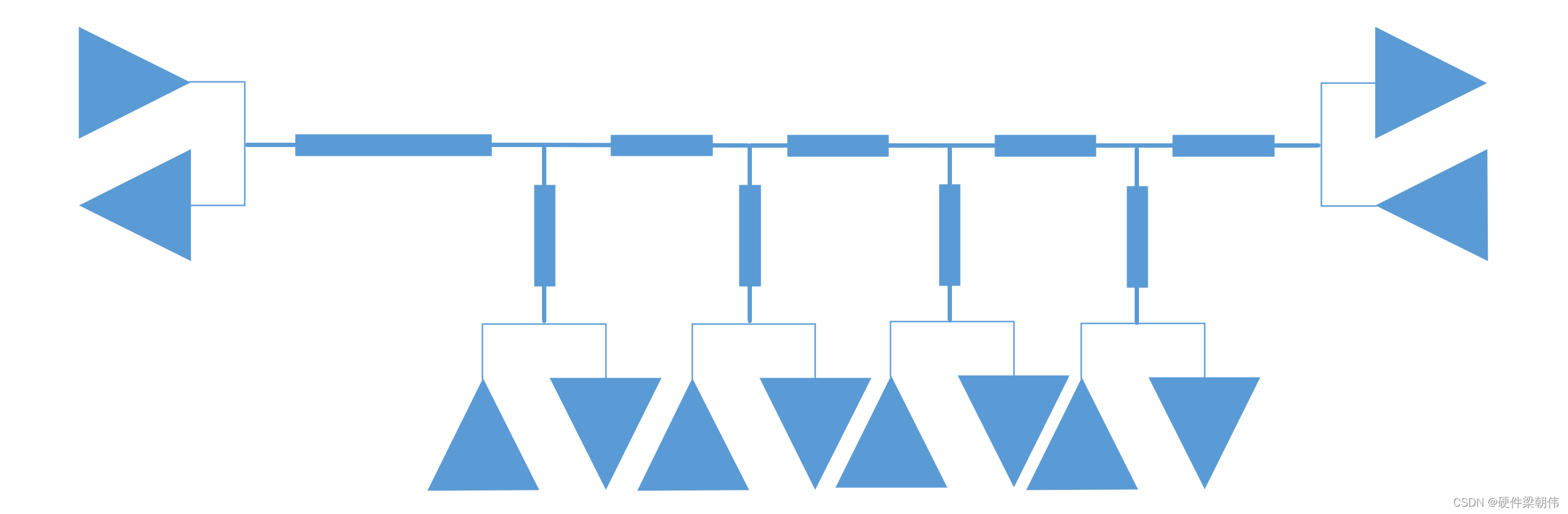

方法F:共源共栅(Cascode)

低压Si MOSFET串联高压SiC JFET,低压管栅极接地,由其承受dVDS/dt,高压管无米勒效应。适合1700V以上超高压应用。

三、桥式电路的特殊处理

在H桥或三相桥中,下管关断时上管开通,dVDS/dt直接耦合至关断管栅极,风险最大。

3.1 负压关断

关断时施加-3V至-5V负压,确保VGS < Vth_min(考虑温度漂移)。即使感应电压+2V,也无法使器件导通。

实现:驱动芯片内置电荷泵,或外接Buck-Boost电路生成负电源。成本增加0.5元,可靠性提升10倍。

3.2 死区时间优化

死区时间t_dead > Trr_max + t_fall_max + 50ns裕量。对于Trr=30ns的SiC MOS,设100ns死区可确保体二极管恢复完成,避免反向恢复电流叠加米勒效应。

3.3 隔离驱动

采用光耦或磁隔离驱动器,将上下管驱动回路电气隔离,避免共地阻抗耦合。CMTI>50kV/μs的隔离驱动器可有效阻断dVDS/dt传播。

四、PCB布局的关键作用

4.1 缩短栅极驱动环路

驱动走线长度<10mm,宽度>0.5mm,与功率地之间距离>5mm。环路电感L_g从20nH降至5nH,感应电压V = L_g×di/dt降低75%。

4.2 地平面完整性

驱动芯片GND与功率MOSFET源极采用开尔文连接,单点接地。避免功率电流在地平面流动时产生压降,耦合到栅极回路。

4.3 屏蔽与隔离

在栅极走线两侧铺地铜皮,形成微带线结构,屏蔽外部电场干扰。对于>200kHz应用,可采用双层板,栅极走线布在内层,上下层均为地平面。

五、器件选型策略

5.1 米勒电容Cgd选型

优先选Cgd<30pF的器件。同规格下,SGT MOS的Cgd比平面栅低60%,SiC MOS低80%。

5.2 阈值电压Vth选择

Vth>3V的器件抗干扰能力更强。Vth=1.5V的逻辑电平MOS易受米勒效应影响,需在驱动端加强抑制。

5.3 封装选择

DFN封装寄生电感<5nH,比TO-247的10nH更优。对于>500kHz应用,优先选无引脚封装。

六、实测验证与调试

6.1 示波器探头选择

使用带宽>500MHz有源探头,接地弹簧<5mm,避免引入额外电感。测量VGS时,探头应紧贴栅极引脚,而非PCB走线末端。

6.2 关键波形判据

VGS:应单调上升/下降,无台阶或回勾。米勒平台宽度应<100ns

VDS:上升沿应平滑,尖峰<0.8×BVDSS

ID:无振荡,di/dt<2A/ns

6.3 参数扫描优化

利用示波器FFT功能,找到振铃频率f_r = 1/(2π√(LC))。在f_r处并联RC吸收(R=√(L/C),C=1/(2πf_rR)),可针对性抑制。

七、工程实践黄金法则

法则一:Rg是抑制米勒效应的“第一功臣”,取值5-50Ω,独立调节开通与关断

法则二:负压关断是桥式电路的“安全锁”,-3V至-5V确保关断可靠性

法则三:有源米勒钳位是“终极保险”,成本仅0.1元,效果媲美负压驱动

法则四:布局优化是“免费午餐”,缩短驱动环路10mm,感抗降低50%

法则五:低Cgd器件是“治本之策”,SGT/SiC技术使米勒效应降低70%

法则六:实测验证是“真理标准”,任何仿真都不能替代示波器波形检查